The Digital Systems and Networks Laboratory is a research centre in the field of integrated circuits design. The VLSI lab is active in a broad range of research areas related to the field of Very Large Scale Integrated circuits, and is strongly committed to the educational mission. Under VLSI laboratory several courses were offered for undergraduate and postgraduate students enrolled in the electronics and communication engineering careers.

The Digital Signal Processing Lab is used by UG and PG students in a core course on Digital Signal Processor and MATLAB Software for designing filters. The Computer Networking Lab is a virtual cluster of multiple networking devices, including servers, clients, routers, switch and firewalls. The servers and network devices are Microsoft and Cisco based respectively. Students train to install, administer and configure clients, server and the network devices that connect them to build network infrastructures for a variety of business needs, from small business to large enterprises.

The Lab has a vivacious activity as is involved in many research projects together with national and international academic and industrial partners, has a wide database of published scientific and technical papers and encourages active collaboration with various institutions aimed at the exchange of students (graduate and PhD) and researchers.

Cadence is a leading provider of EDA and semiconductor IP. The custom/analog tools help engineers design the transistors, standard cells, and IP blocks that make up SoCs. The digital tools automate the design and verification of giga-scale, giga-hertz SoCs at the latest semiconductor processing nodes. The IC packaging and PCB tools permit the design of complete boards and subsystems. Cadence also offers a growing portfolio of design IP and verification IP for memories, interface protocols, analog/mixed-signal components, and specialized processors. And reaching up to the systems level, Cadence offers an integrated suite of hardware/software co-development platforms. The system-on-chip (SoC) designs integrate complex analog and digital blocks, requiring thorough testing and analysis of how analog and digital circuits interact and the influence they have on each other. Cadence mixed-signal simulation solution combines the industry-leading digital and analog circuit simulators: Xcelium and Spectre, to provide designers and verification engineers superior performance and accuracy required for designs.

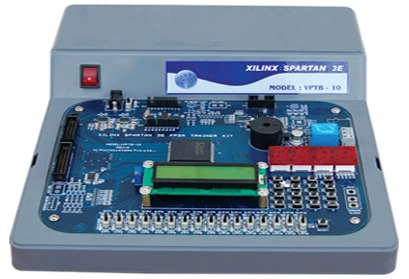

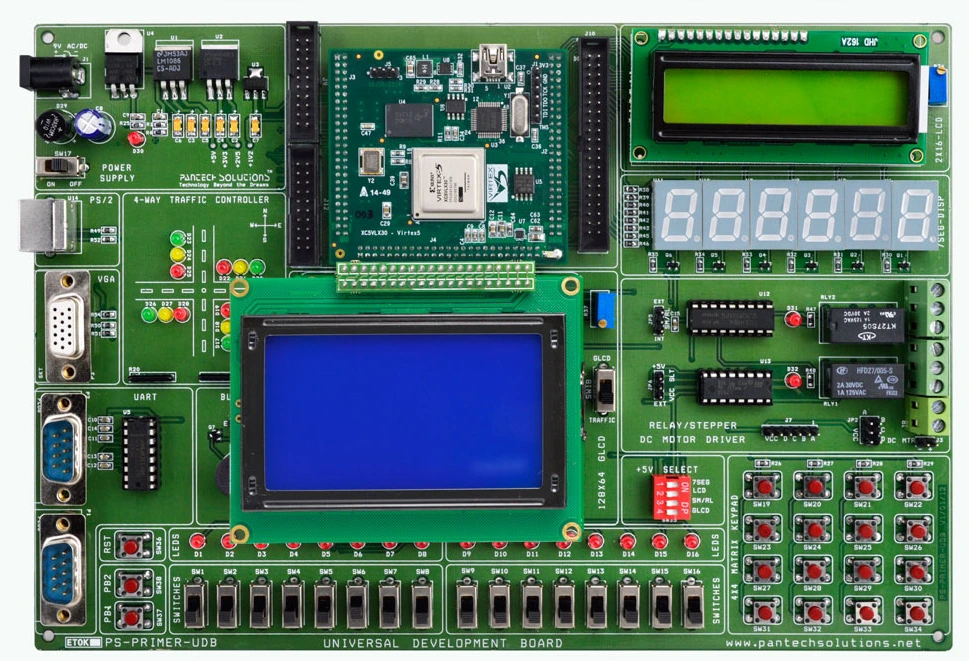

One Reset Switch, one switch is provided for giving manual clock FPGA configuration through, JTAG Port, on board Flash Prom XCF02S, On board programmable PLL oscillator from 1 MHz to 100 MHz using jumpers,4 Nos of 7 segment LED display, one relay and Buzzer provided, Stepper & DC motor Driver provided, 4 * 4 matrix key provided, housed in a sleek plastic cabinet with built in SMPS 5V/2A, Compatible with Xilinx ISE Design Suite Web PACK Software, on board USB to JTAG is available for configure FPGA.

16 Nos. of Point LEDs (Logic Output), 16 Nos. of Slide Switches (Digital Input), 4X4 Matrix Keypad, 2X16 Character LCD (Background Light), 6 Nos. 7-Segment Display, Stepper Motor Interface, 2 Nos. of SPDT Relay, 2 Nos. of UART(RS232), 3-Bit VGA Interface, 5V Buzzer, Traffic Light controller Module, PS/2 (Keyboard Interface), 2-Numbers of 20-Pin Expansion Connector, 40-Pin Expansion Connector, PWM with DC Motor,128×64 GLCD Module, Clock 50MHz

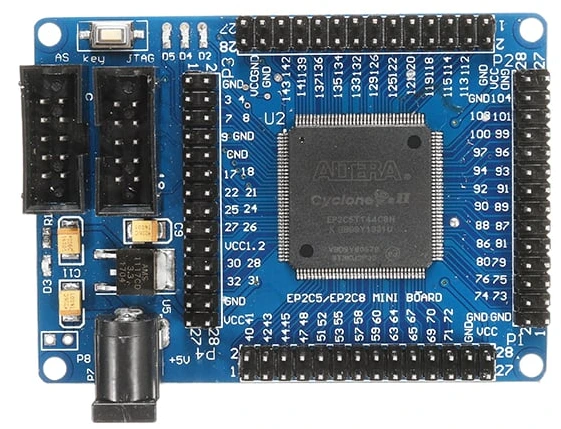

On-board EP2C5T144 chip, EPROM chip configuration using EPCS4, the size of 4Mbit,Onboard 50M active patch crystal (Crystal Slaughter halfback), Power supply with a largemouth outlet, single 5V power supply, Board has power indicator and resets switch On-board 3 SMD LED, the LED test can be done an experiment, more experiments using lead to complete, More IO ports and clock pins through the pin leads through these interfaces can be extended to any memory and peripherals, Board using high-quality tantalum capacitor power filter, Support Nios II embedded CPU development.

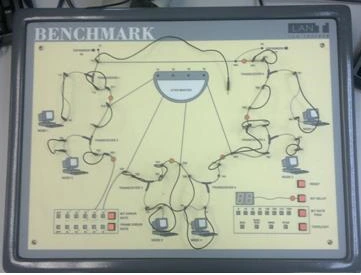

Comprehensive set of experiments to observe and measure the behaviour of several LAN protocols: MAC layer, Data link layers and connection management, User configurable data rates, Generation of bit errors and Frame errors between nodes, Variable Network size with each NEU, NEUs can be cascaded to increase the network size, Emulation of two nodes by each PC, Halves the number of PCs required, User configurable delays between nodes, allows programming of all experiments from scratch using the library, for more in-depth exposure, Menu driven user interface to experiments.

PC to PC communication with IEEE 802.3, Peer to Peer network, Client - Server network Design of Star topology using 100Base-Tx, Design of Bus topology using 10Base-2 Design of Ring topology using DB9, Creation of cables for network connections Socket programming and processing, Data Encryption and Decryption, Various LAN Protocols, Data rate up to 100Mbps, Variable packet size, Variable packet delay, Error generation (Manual and Auto), Switch faults in both hardware and software.

.webp)

48K X 16 bit EPROM for monitor, 16K X 16 bit RAM for user program memory, 32K X 16 bit RAM for user data memory, 1 No.of AD-1674 @ 10 s conversion speed, Analog Input : ±5 volt, 1 No.of DAC using AD 7521/DAC 1220 @ 3s setting time, DAC output ±5 volts, One RS232 interface for host support terminated at 9 pin ‘D connector, 12/14/16 bit ADC & DAC through VDSP-link Bus, Additional Hardware Expansion through VDSP-link Bus.+5V/3.0A, ±12V/150mA with short circuit protection, one 12 Bit single Channel ADC with 100KHz sampling rate, One 12 Bit single channel DAC.

.webp)

Highest performance floating point Digital signal processor, 150 MHz Clock rates 6.7ns Instruction cycle time, 16 bit external memory interface,16 bit Host-port interface, 2 multichannel Audio & Buffered serial ports, Inter integrated circuit Module, data cache On-chip Memory, cache mapped RAM On-chip Memory, FLASH for monitor Program, SDRAM for External Memory, 8 way DIP switches & LEDs to user interface, LCD interface, Stepper motor Interface, On board USB and UART for serial communication, PCM3002 Audio codec.

Embedded processing design support for the Zynq-7000 SoC family, The industry's fastest timing closure with Xilinx Smart Compile technology Complete, front-to-back design environment, including the Xilinx CORE Generato system and the full Plan Ahead design and analysis tool, Integrated HDL verification with the Lite version of the ISE Simulator (ISim).

ModelSim simulates behavioural, RTL, and gate-level code - delivering increased design quality and debug productivity with platform-independent compile. Single Kernel Simulator technology enables transparent mixing of VHDL and Verilog in one design. The ModelSim-Altera Edition software is licensed to support designs written in 100 percent VHDL and 100 percent Verilog language and does not support designs that are written in a combination of VHDL and Verilog language, also known as mixed HDL. Mixed HDL support is available in the PE and SE versions of ModelSim from Mentor Graphics. ModelSim-Altera Edition only supports Altera gate-level libraries. The ModelSim-Altera Edition software includes all ModelSim PE features, including behavioural simulation, HDL test benches, and tool command language (Tcl) scripting.